728x90

반응형

SMALL

🔍 서론: 왜 반도체 ‘패키징’ 기술이 중요한가?

반도체 산업은 나노미터(nm) 단위의 미세 공정만으로 이루어져 있다고 생각하기 쉽습니다. 하지만 칩을 보호하고, 전기적 신호를 외부로 전달하며, 냉각을 도와주는 ‘패키징’ 기술은 반도체의 성능과 수명을 좌우하는 핵심 공정입니다.

이 글에서는 반도체 패키징 기술의 역사, 주요 전환점, 그리고 미래 전망까지 총정리해 보겠습니다.

📘 반도체 패키징 기술의 발전 연대기

연대 패키징 기술 특징 및 혁신 포인트 키워드

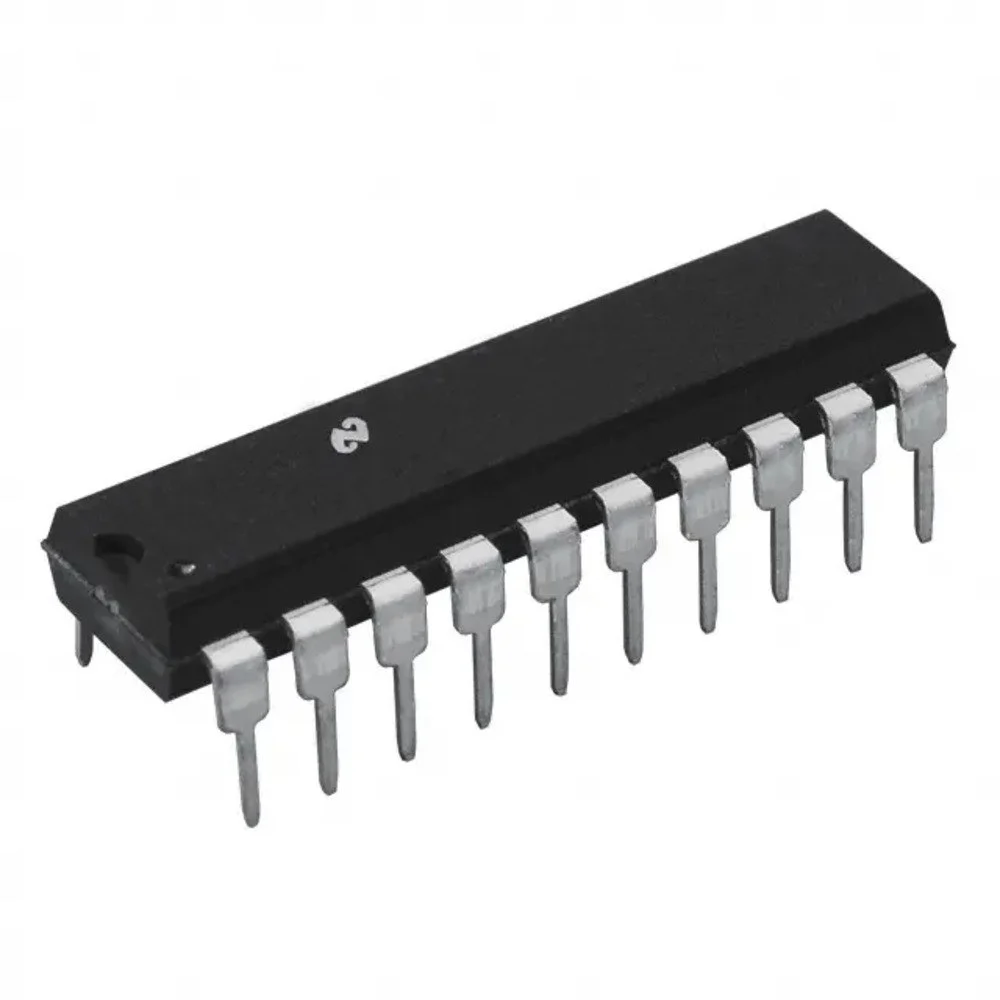

| 1960년대 | DIP (Dual In-line Package) | 플라스틱/세라믹 케이스에 칩을 삽입하여 핀을 양쪽에 배치 | 초기 패키징 |

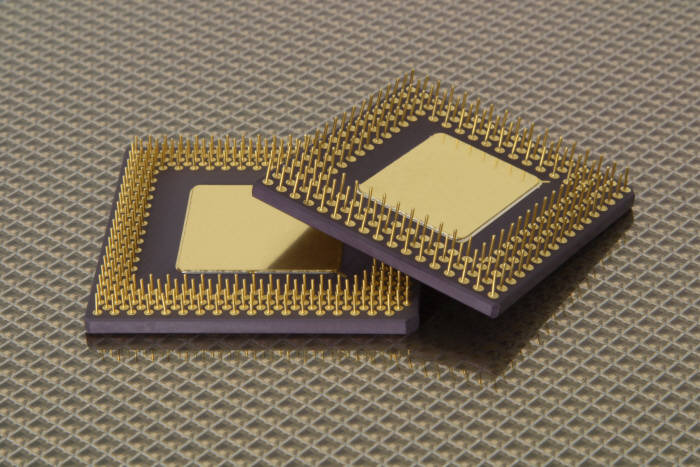

| 1970년대 | QFP, PGA | 고집적화 요구에 따른 핀 수 증가, 열방출 개선 | 표면실장(SMT) |

| 1980년대 | BGA (Ball Grid Array) | 핀 대신 볼을 하부에 배치, 고밀도/고속화 대응 | 고집적 패키징 |

| 1990년대 | CSP (Chip Scale Package) | 칩 크기와 거의 동일한 소형화 패키지 | 모바일 기기 |

| 2000년대 | SiP, MCM | 여러 칩을 하나로 통합해 복합 기능 구현 | 시스템 인 패키지 |

| 2010년대 | 2.5D/3D 패키징 | TSV를 활용한 칩 적층 구조, 고속 인터커넥트 | HBM, 3D NAND |

| 2020년대 | FOPLP, AI 패키징 | 패널레벨·팬아웃·AI 최적화 패키징, 열 제어 기술 중요 | AI 반도체, 고성능 컴퓨팅 |

🔧 주요 패키징 기술별 개요

🧊 BGA (Ball Grid Array)

- 장점: 높은 핀 수, 우수한 방열성, 자동화 가능

- 적용 분야: PC, 서버, 통신 장비

🧩 CSP (Chip Scale Package)

- 장점: 크기 소형화, 경량화, 모바일 최적화

- 적용 분야: 스마트폰, 태블릿, IoT

🧱 3D 패키징

- TSV (Through-Silicon Via): 칩을 수직으로 연결해 데이터 병목 제거

- HBM (High Bandwidth Memory): AI 반도체의 핵심 기술

🧠 첨단 패키징 (Advanced Packaging)

- FOPLP (Fan-Out Panel Level Packaging): 칩 경계 초월 인터커넥션

- CoWoS, EMIB (Intel, TSMC 기술): 고성능 패키징의 선두주자

🌐 주요 기업의 패키징 기술 전략

기업 전략 기술 특징

| TSMC | CoWoS, InFO | AI/GPU용 고대역 기술, 애플 M시리즈에도 활용 |

| 삼성전자 | I-Cube, H-Cube | 고성능 서버용 반도체 패키지 강화 |

| Intel | EMIB, Foveros | 칩렛 구조 기반 고성능 CPU 구현 |

| ASE | SiP, Fan-Out | 종합 패키징 서비스 리더 |

📈 반도체 패키징 기술의 미래

트렌드 설명

| 📊 AI 최적화 패키징 | 고대역 메모리(HBM)와 GPU 연계 |

| 🔌 칩렛 (Chiplet) 기반 구조 | 다양한 기능 칩을 모듈화 |

| 🌿 지속가능한 소재 | 친환경 패키징 소재 채택 증가 |

| 🧊 고효율 열 제어 기술 | 방열 솔루션을 통합한 설계 확산 |

🏁 결론: 패키징이 반도체의 미래를 결정한다

미세 공정만큼이나 중요한 것이 바로 패키징 기술입니다. 과거 단순한 보호 수단이던 패키징은 이제 성능을 향상시키는 핵심 기술로 거듭났습니다. 특히 AI, 자율주행, 데이터센터 시대에는 패키징 기술력이 반도체 경쟁력 그 자체가 되고 있습니다.

앞으로도 반도체 패키징은 고성능, 저전력, 소형화라는 삼박자를 갖춘 혁신의 주역으로 진화할 것입니다.

🔑 주요 키워드 (SEO 최적화)

- 반도체 패키징 기술 발전

- 첨단 패키징 종류

- 3D 반도체 패키지

- HBM과 TSV

- FOPLP, 칩렛

- 반도체 패키징 업체 순위

- TSMC CoWoS vs Intel EMIB

728x90

반응형

LIST